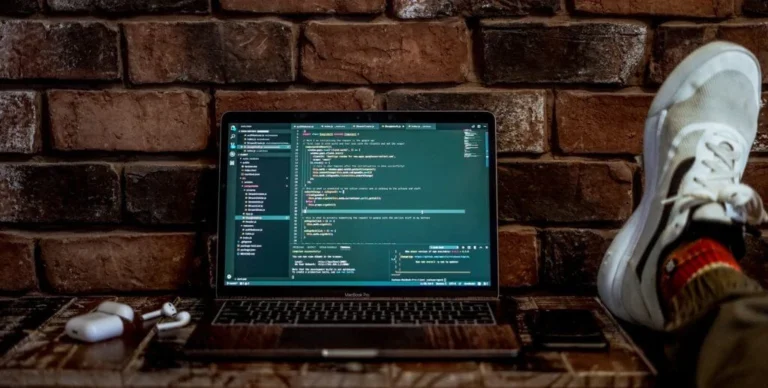

On this page you will find a series of Verilog tutorials that introduce FPGA design and simulation with Verilog. These Verilog tutorials take you through all the steps required to start using Verilog and are aimed at total beginners.

Verilog Video Tutorials

For a deeper dive, our exclusive Verilog video tutorials offer a deeper dive into the subjects covered in our free Verilog tutorials. The video tutorials include live coding sessions with source code that will be shared with anyone that purchases a video.

A new company called Fourdotpay will be handling payments for our Verilog video tutorials. Anyone who signs up with them during this introductory period will receive a £5 welcome bonus. This means you can try out one of our new videos absolutely free. See our FAQS page for details about how to take advantage of this offer.

Our partners at the Fourdotday payment portal would really appreciate any feedback you have on their platform. For feedback on the Fourdotpay platform, please contact richard@fourdotzero.io.

Video Tutorials

An Introduction to Data Types in Verilog

Using Continuous Assignment to Model Combinational Logic

Find the source code from this video tutorial on EDA Playground